在半导体产业链中,芯片可靠性测试是验证产品寿命与稳定性的核心步骤。随着应用场景向汽车电子、工业控制及人工智能领域扩展,客户对于芯片在极端环境下的表现提出了更高要求。许多企业在送测前往往面临标准选择困难、测试项目不明确以及失效分析流程复杂等疑问。针对这些高频问题,本文将对芯片可靠性测试的关键环节进行详细梳理,帮助研发与质量团队建立清晰的测试认知,确保产品交付质量符合行业预期。

测试标准与规范依据

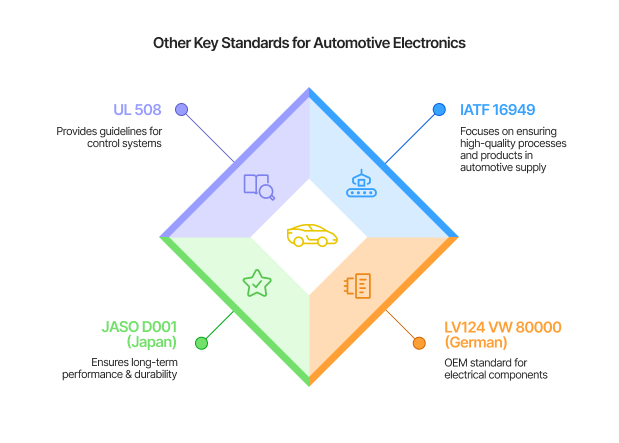

不同应用领域的芯片需遵循不同的可靠性标准体系。车规级芯片通常参照 AEC-Q100 系列标准,该标准针对集成电路应力测试认证制定了严格要求,涵盖环境温度、工作寿命及封装完整性等多个维度。工业级与消费级产品则多采用 JEDEC 标准,如 JESD22 系列,其中定义了具体的测试方法与条件。此外,部分客户会根据特定使用场景制定企业内部标准,这要求测试机构具备灵活的标准转化能力,将通用规范转化为可执行的测试方案。

在选择标准时,需明确芯片的目标市场。例如,进入汽车供应链必须通过 AEC-Q100 Grade 0 至 Grade 3 的相应等级认证,而消费类电子产品可能仅需满足基本的温湿度测试要求。标准的选择直接决定了测试项目的覆盖范围与通过难度。

核心测试项目解析

可靠性测试包含多种应力试验,旨在模拟芯片在全生命周期内可能遇到的极端条件。常见的项目包括高温工作寿命测试(HTOL)、高温高湿偏压测试(HAST)以及温度循环测试(TC)。这些项目分别针对电迁移、腐蚀疲劳及热膨胀系数不匹配等潜在风险。

下表列出了几种关键测试项目及其主要目的:

| 测试项目 | 典型条件 | 主要检测失效机理 |

|---|---|---|

| HTOL (高温工作寿命) | 125°C, 1000 小时 | 电迁移、热载流子注入 |

| HAST (高温高湿偏压) | 130°C, 85% RH, 96 小时 | 封装腐蚀、分层 |

| TC (温度循环) | -65°C 至 150°C, 1000 次 | 焊点疲劳、界面开裂 |

| ESD (静电放电) | HBM/CDM 模型 | 栅氧化层击穿、金属熔融 |

针对特定封装形式,如 BGA 或 QFN,还需增加板级可靠性测试,以验证焊点在 PCB 上的结合强度。测试项目的组合需根据芯片结构特点进行定制,避免过度测试造成成本浪费或测试不足留下质量隐患。

失效机理与故障定位

当测试过程中出现失效样品时,快速定位根本原因是关键。常见的失效机理包括介质击穿、金属互连断裂及封装分层。失效分析通常结合非破坏性与破坏性手段,如 SAT 超声波扫描可检测内部分层,SEM 扫描电镜能观察微观结构损伤。

在进行故障定位时,需结合电性测试数据与物理分析结果。例如,若漏电流异常增大,可能指向栅氧化层损伤;若功能间歇性失效,则可能与焊点裂纹有关。专业的失效分析团队能够通过交叉验证,缩短问题排查周期,为设计改进提供确切依据。

测试周期与样品要求

测试周期取决于所选项目的累积时间。标准的 HTOL 测试通常需要 1000 小时,加上中间读数时间,整体周期约为 45 至 60 天。若包含失效分析环节,时间会相应延长。样品数量需满足统计学要求,一般每个测试组别需准备 77 颗以上样品,以确保置信度。

送测前需确认样品状态,包括晶圆批次、封装形式及引脚定义。测试机构通常会要求提供详细的测试向量文件,以便在动态老化过程中监控芯片功能状态。充分的前期准备能有效避免因样品不足或文件缺失导致的测试中断。

测试价值与质量保障

可靠性测试不仅是合规的必要条件,更是提升产品竞争力的手段。通过严格的应力筛选,能够提前暴露设计缺陷与工艺波动,降低市场返修率。对于车规及医疗等高安全等级领域,完善的测试数据是获得客户信任的基础。企业应建立从设计阶段开始的可靠性评估流程,将测试反馈融入迭代优化中,从而构建坚实的质量屏障。

关于上海德垲检测

上海德垲检测作为专业的第三方检测机构,深耕半导体测试领域,具备完善的芯片可靠性测试与失效分析能力。公司拥有符合 JEDEC 及 AEC 标准的高温老化房、温湿度试验箱及高精度电测设备,可承接从晶圆级到成品级的全流程测试任务。技术团队经验丰富,能够针对复杂芯片结构定制测试方案,并提供专业的测试开发支持。在设备优势方面,实验室配备了先进的 SAT、X-Ray 及 FIB 切片设备,确保失效定位的精准度与效率。

欢迎联系专业工程师,获取针对性的测试方案咨询与报价服务,助力您的芯片产品顺利通过可靠性验证。