芯片测试质量控制方法与关键流程解析

深入探讨芯片测试质量控制方法,涵盖测试流程规范制定、失效分析技术应用、可靠性评估标准执行及数据管理策略优化。帮助半导体企业提升测试精度,有效降低不良率,确保芯片产品符合行业高标准要求。结合先进检测设备与专业团队,解决复杂测试难题,为芯片稳定性提供坚实依据,助力企业通过车规级认证,提升市场竞争力。

深入探讨芯片测试质量控制方法,涵盖测试流程规范制定、失效分析技术应用、可靠性评估标准执行及数据管理策略优化。帮助半导体企业提升测试精度,有效降低不良率,确保芯片产品符合行业高标准要求。结合先进检测设备与专业团队,解决复杂测试难题,为芯片稳定性提供坚实依据,助力企业通过车规级认证,提升市场竞争力。

芯片测试开发周期受产品复杂度、方案成熟度及硬件准备影响较大。本文详细解析测试方案制定、硬件设计、程序调试及验证释放等核心阶段耗时,并提供不同类型芯片的参考时间表。了解影响进度的关键变量,有助于企业合理规划项目节点,优化上市流程,确保测试质量与效率平衡。

芯片测试成本直接影响产品最终利润率与市场竞争力。本文深入解析降低测试费用的五大核心策略,涵盖测试方案早期优化、设备利用率提升、覆盖率平衡及外包决策分析。通过科学规划与专业技术支持,帮助企业在保证质量的前提下有效控制预算,实现半导体测试环节的经济效益最大化,助力研发落地。

HAST 高温高湿测试是评估电子元件可靠性的关键方法,通过高温高湿高压环境加速老化。本文详解测试原理、主流国际标准及流程,帮助工程师理解未饱和高压蒸汽恒定湿热试验对芯片封装的影响及失效分析要点。适用于半导体封装验证,确保产品在严苛环境下的长期稳定性与寿命评估,为研发提供数据支持。

芯片测试一站式解决方案涵盖从设计验证到量产可靠性评估的全流程服务。本文深入解析半导体测试关键流程、主流国际检测标准及失效分析方法,帮助企业在研发阶段精准识别潜在风险,显著提升产品良率与市场竞争力,确保芯片性能长期稳定可靠,满足车规级及工业级应用需求。

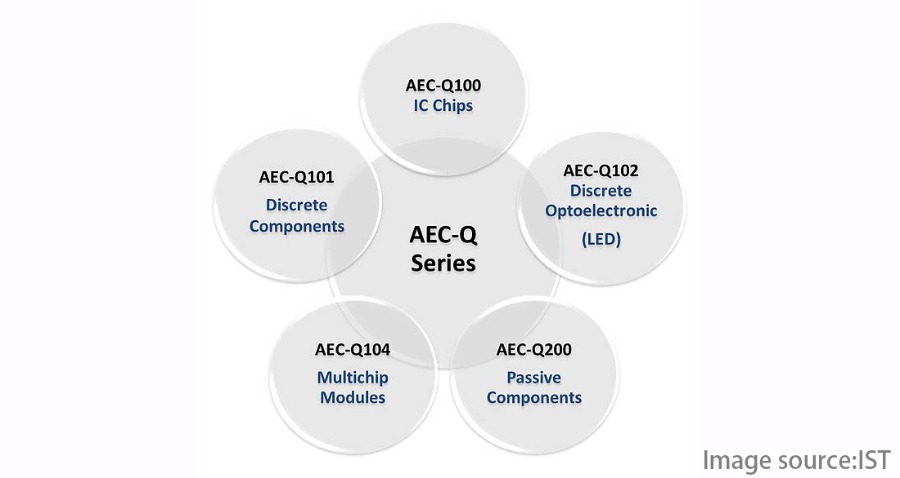

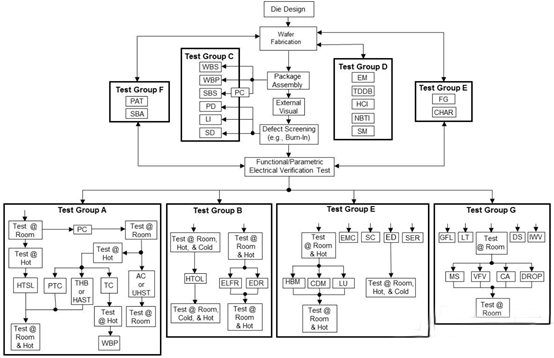

本文深度解析芯片可靠性测试标准,涵盖 JEDEC 规范与 AEC-Q100 车规认证要求。介绍集成电路应力测试鉴定流程及抗 Latch Up 能力评估方法,为半导体工程师提供权威参考,确保芯片在极端条件下的稳定运行与质量合规。

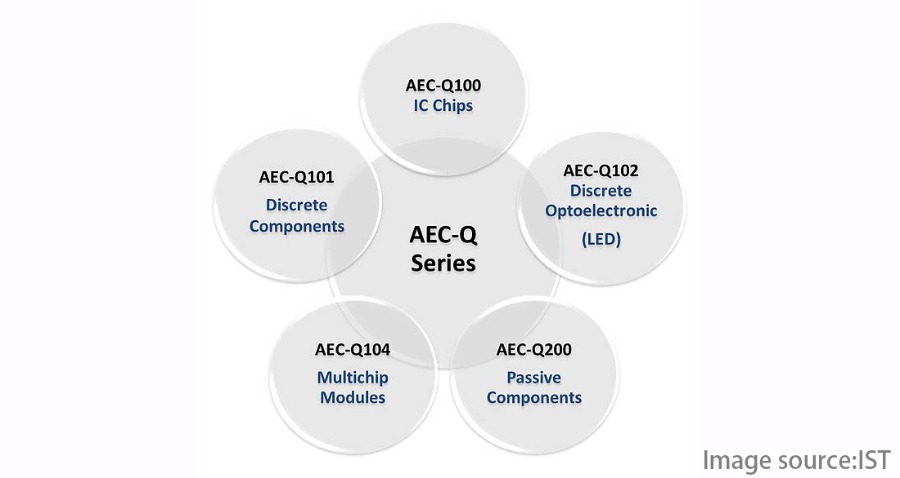

AEC-Q测试是汽车电子组件可靠性压力验证过程,但不等于正式认证。官方无AEC认证机制,供应商需自执行测试并提交数据证明合规。本文剖析二者区别、流程及误解,帮助芯片供应商避免陷阱,确保产品顺利进入汽车供应链。

AEC-Q100是汽车电子理事会制定的集成电路可靠性资格标准,确保芯片在高温、高湿等极端条件下稳定工作。本文详解其定义、等级划分、适用芯片类型如传感器和电源管理芯片,以及测试方法与认证流程,帮助芯片设计师和汽车制造商了解车规级检测的重要性,提升产品安全与性能。

深入解析洁净度对芯片可靠性测试结果的影响,重点分析颗粒污染如何引发短路、漏电等失效,并介绍实验室ISO洁净室等级管理标准与实践要求。关键词:可靠性测试环境, 洁净室, 芯片可靠性测试。

详解OBIRCH(光束诱导电阻变化)技术在芯片失效分析中的应用,涵盖工作原理、激光参数设置、信号处理技巧与定位精度优化方法,助力工程师高效锁定内部短路故障。关键词:芯片失效分析, OBIRCH, 短路定位。

实用指南教你选择芯片可靠性测试设备,涵盖ATE平台、高温老化炉选型与预算策略,提升测试效率与质量。

探讨半导体测试培训的重要性,介绍如何通过培训提升芯片测试技能,助力5G、AI芯片开发。

注意:每日仅限20个名额

扫码咨询

广州分公司

地址:广州市黄埔区云埔街源祥路96号弘大商贸创意园5号楼605房

深圳分公司

地址:深圳市坪山区碧岭街道碧岭社区坪山金碧路543号忠诚科技大厦801B

上海分公司

地址:上海市奉贤区星火开发区莲塘路251号8幢

芜湖分公司

地址:安徽省芜湖市镜湖区范罗山街道黄山中路金鼎大厦1411