在芯片和PCB设计领域,高速信号传输已成为主流,但随之而来的是反射、串扰、抖动等完整性问题。这些问题往往在后期测试或量产阶段暴露,导致多次迭代、原型重制和故障修复,试错成本居高不下。信号完整性(Signal Integrity,简称SI)测试通过早期介入,能显著减少这些隐形成本。根据行业分析,SI测试可将设计迭代成本降低20-50%,帮助企业加速上市并提升竞争力。本文将量化SI测试的成本节省潜力,并提供实践指导。

SI测试的概念与作用

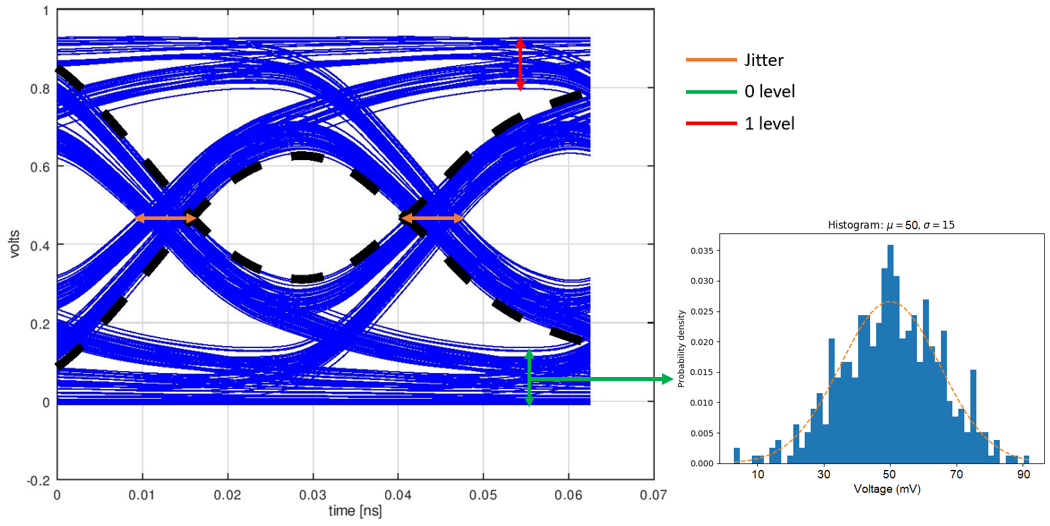

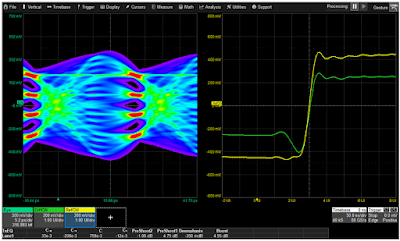

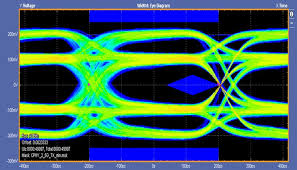

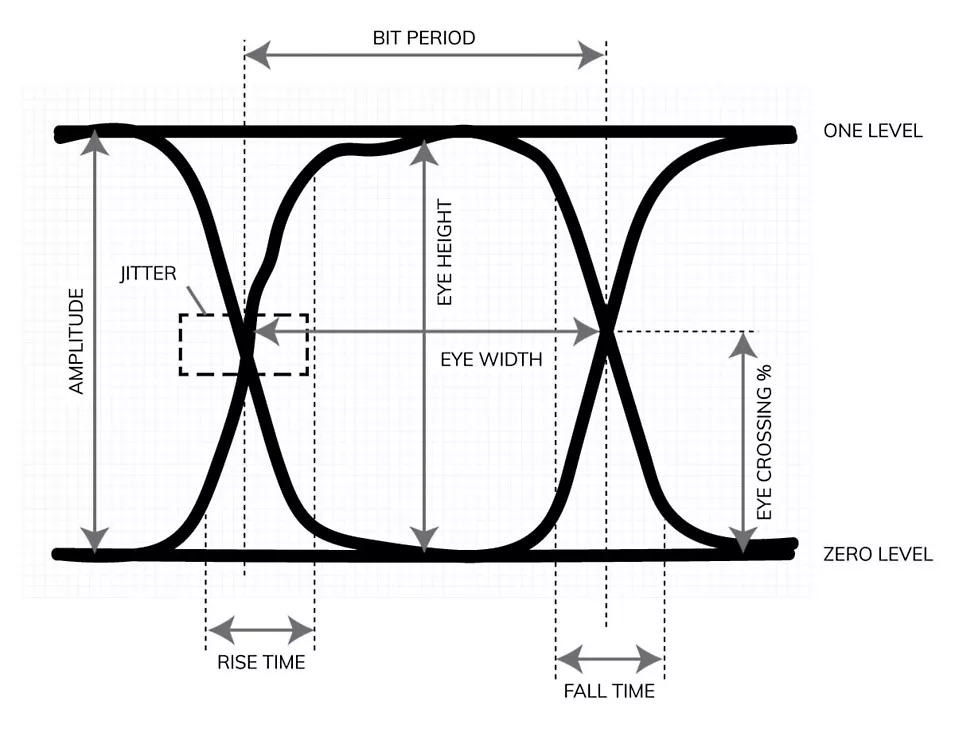

信号完整性测试评估高速信号在传输路径中的质量,确保波形不因物理因素失真。它包括时域(如眼图分析)和频域(如S参数测量)方法,核心指标有眼高/眼宽、抖动、插入损耗(IL)和回波损耗(RL)。

SI测试的作用在于预测问题,避免盲目试错。在设计早期应用,能发现阻抗不匹配或串扰隐患,减少物理原型迭代。以下是SI问题影响示意图:

SI测试减少试错成本的机制

SI测试通过仿真与实测结合,在虚拟环境中模拟信号行为,及早识别风险,从而减少实际试错环节。主要机制包括:

- 早期问题检测:仿真阶段捕捉反射或损耗,避免后期硬件调试。

- 迭代优化:基于测试数据快速调整布局,缩短设计周期。

- 风险降低:减少场外故障和召回,节省支持与维护成本。

- 资源高效:降低原型制作和测试设备占用,优化人力分配。

这些机制将试错从“物理实验”转向“数据驱动”,显著压缩成本。更多SI基础知识,可参考信号完整性测试概述。

量化估算:SI测试能减少多少成本

根据行业报告和案例,SI测试可大幅降低试错成本。具体量化如下:

- 设计迭代减少:传统试错需3-5轮原型,SI测试可减至1-2轮,节省50-70%迭代费用。

- 总体成本节约:早期SI介入可降低整体项目成本20-50%,包括原型制作(占30%)、调试时间(占40%)和潜在召回(占20%)。

- ROI示例:投资1万元SI测试设备和服务,可节省5-10万元后期修复成本,ROI达400-900%。

以下表格总结典型节省比例(基于PCB和芯片项目数据):

| 成本类别 | 无SI测试成本占比 | SI测试后节省比例 | 示例节省金额(中型项目) |

|---|---|---|---|

| 原型制作 | 30% | 40-60% | 减少5-8万元 |

| 调试与返工 | 40% | 50-70% | 减少10-15万元 |

| 场外故障 | 20% | 30-50% | 减少3-5万元 |

| 总计 | 100% | 40-60% | 节省20-30万元 |

这些估算源于实际工程实践,具体取决于项目复杂度。

SI测试的方法与工具

SI测试方法多样化,确保高效成本控制:

- 仿真方法:使用HyperLynx或ADS软件,预分析信号路径,成本低、迭代快。

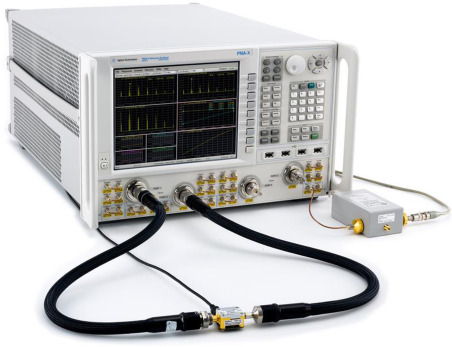

- 实测方法:高带宽示波器和VNA采集眼图/S参数,验证仿真结果。

- 集成流程:从布局优化到封装测试,全链路覆盖。

这些方法结合使用,能将试错风险降至最低。眼图解读可参考高速信号眼图解读。

应用领域

SI测试在以下领域体现成本节省价值:

- 高速芯片:PCIe Gen6、USB4,确保接口兼容,减少认证失败成本。

- 5G/通信:射频模块,优化损耗,缩短上市周期。

- 汽车电子:ADAS芯片,防范环境干扰,降低召回风险。

- 数据中心:服务器SoC,控制串扰,提升整体效率。

这些应用中,SI测试的投资回报尤为显著。

测试步骤详解

标准SI测试流程,旨在最大化成本效益:

- 需求评估:定义速率、裕度阈值。

- 预仿真:建模互连,初步优化。

- 样品准备:制作测试板。

- 实测执行:采集数据,比对标准。

- 分析优化:计算裕度,提出改进。

- 验证迭代:重测确认,量化节省。

此流程可将试错循环压缩30-50%。

真实案例分享

- PCIe芯片项目:某厂商忽略SI,3轮原型后仍抖动超标,成本超支15万元。引入SI测试后,1轮优化即达标,节省60%迭代费。

- 5G模块案例:反射问题导致返工,初始成本8万元。SI仿真及早发现,减少到3万元,节省62.5%。

这些案例证明SI测试的实际经济价值。

常见问题解答

- SI测试初始投资高吗? 入门级工具几千元,远低于试错损失。

- 如何计算具体节省? 用ROI公式:(节省成本 – 测试投资)/测试投资 × 100%。

- 适用于小项目吗? 是,即使小型芯片也能减少20%成本。

- 与PI测试结合? 推荐,联合可放大节省效果。

总结

信号完整性测试通过早期检测和优化,能显著减少试错成本,行业估算达20-50%,甚至更高,涵盖迭代、返工和故障环节。从机制到案例,本文展示了其经济价值,帮助您评估投资。

如果您的项目面临高速信号挑战或需成本优化,上海德垲芯片检测(https://www.jiancechip.com)提供咨询+报告服务、行业标准支持以及定制化测试方案,欢迎联系获取详细评估。