在芯片设计与制造领域,随着5G、AI、边缘计算和高速数据中心的迅猛发展,芯片内部和外部信号传输速率已从Gbps级跃升至数十甚至上百GT/s。信号完整性(Signal Integrity,简称SI)测试作为评估高速信号质量的核心手段,正受到前所未有的重视。过去,低速芯片可忽略SI问题,但如今忽略它可能导致产品失效、返工成本飙升或市场竞争力下降。本文将探讨SI在芯片测试中日益重要的原因、关键概念及实践应用,帮助工程师把握这一趋势。

SI的基本概念

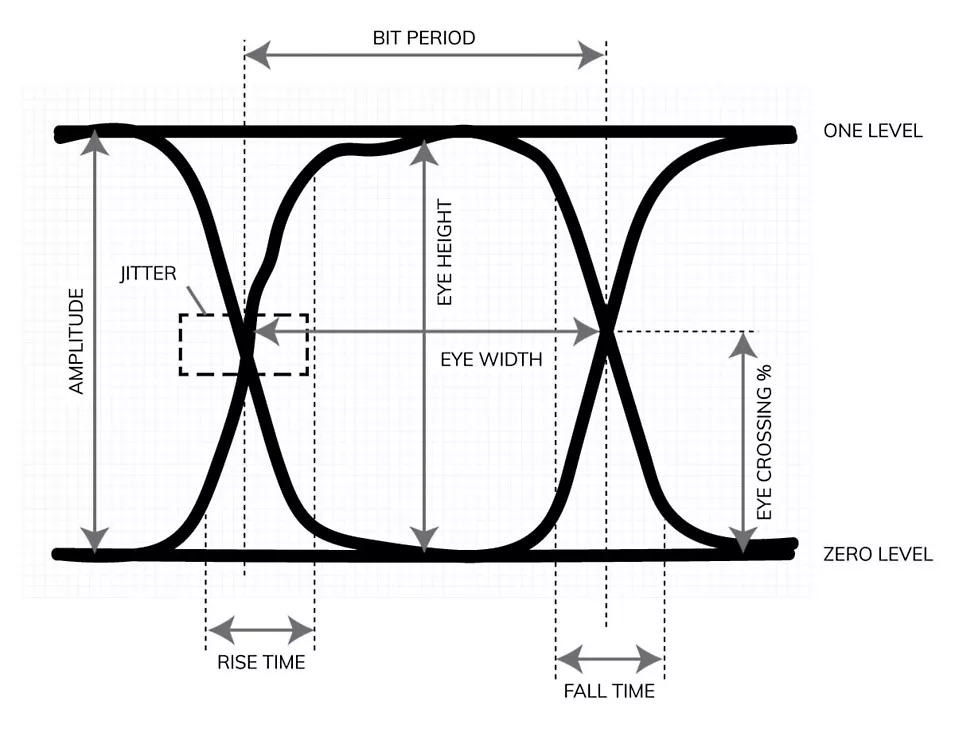

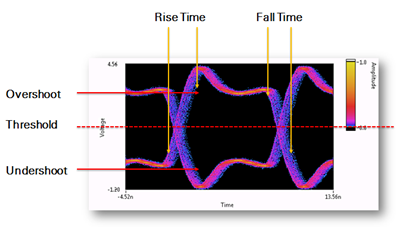

信号完整性是指高速信号在芯片内部互连、封装、PCB走线等路径中保持波形形状、时序和幅度的能力。它关注反射、串扰、抖动、损耗等物理效应,确保信号不失真。SI测试通过量化这些效应,验证芯片是否在高频环境下可靠运行。

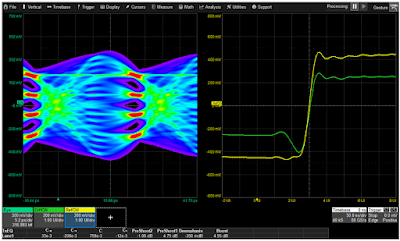

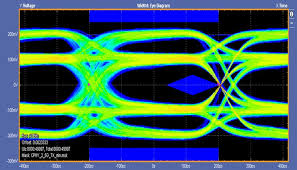

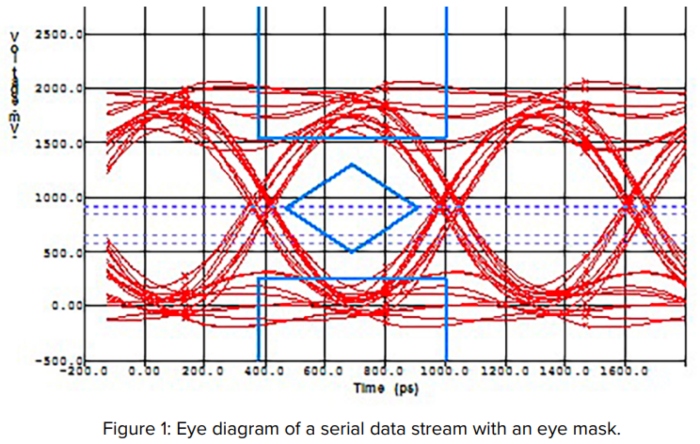

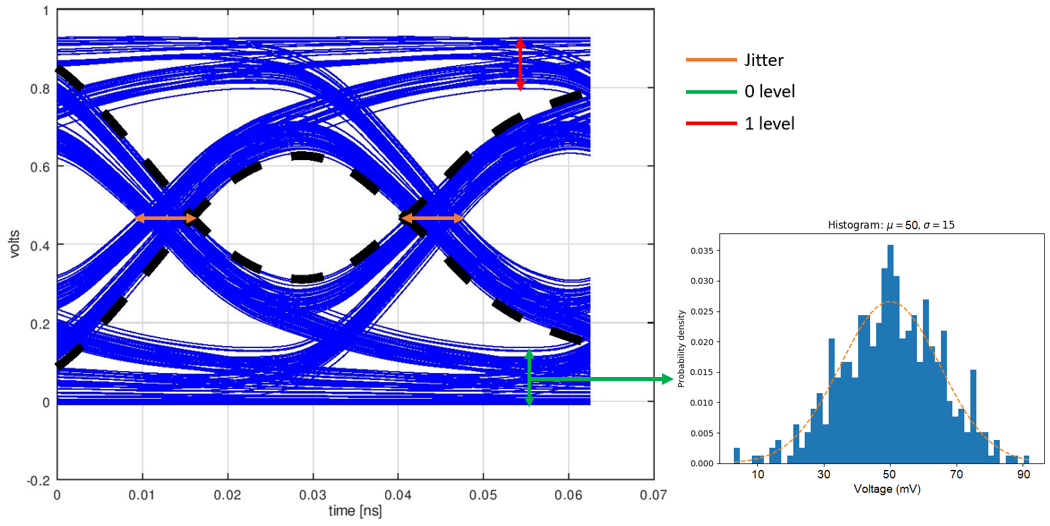

简单来说,SI就像芯片信号的“健康体检”,防止数据错误率上升或系统崩溃。以下是典型SI问题示意图:

为什么芯片测试中越来越重视SI

芯片技术演进推动SI从辅助测试转向核心验证。主要原因包括:

- 传输速率爆炸式增长:从DDR4的3.2 GT/s到DDR5的8.8 GT/s,再到PCIe Gen6的64 GT/s,高边沿速率放大寄生效应,传统测试不足以覆盖。

- 集成度与复杂性提升:SoC芯片集成多核、多接口,内部互连密集,串扰和噪声风险激增。

- 功耗与热管理挑战:低功耗设计压缩信号幅度裕度,SI问题易引发功耗异常。

- 系统级互操作需求:芯片需兼容多厂商生态,未优化SI导致链路失败或EMC不合规。

- 成本与时间压力:后期调试SI问题成本是设计阶段的10-100倍,及早重视可加速上市。

这些因素使SI测试成为芯片从仿真到量产的必备环节,忽略它等同于冒险。更多SI基础,可参考信号完整性测试概述。

SI问题的影响与风险

未重视SI可能造成:

- 性能下降:眼图闭合导致误码率(BER)>10^-12,数据重传增加延迟。

- 可靠性故障:抖动累积引发时序违规,芯片在高温或老化后崩溃。

- 经济损失:产品召回或调试延期,成本占总预算20%以上。

- 市场风险:不符合USB-IF或PCI-SIG标准,无法认证上市。

及早SI测试可将风险降至最低,确保芯片稳定。

SI测试的种类与方法

SI测试分为时域和频域两大类:

时域测试

- TDR/TDT:评估阻抗连续性和反射。

- 眼图分析:叠加波形,测量眼高/眼宽/抖动。

频域测试

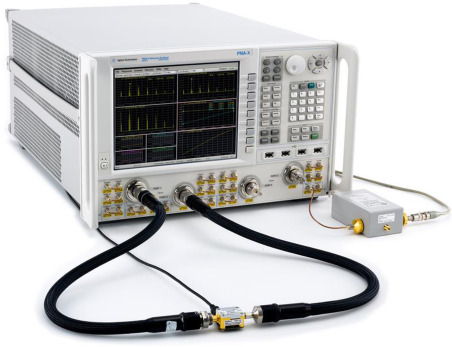

- VNA:测量S参数,如插入损耗(IL)和回波损耗(RL)。

方法结合仿真(HyperLynx/ADS)和实测,使用高带宽示波器。眼图是核心工具,详见高速信号眼图解读。

应用领域

SI测试广泛应用于:

- 高速接口芯片:PCIe、USB4,确保链路裕度。

- 内存芯片:DDR5/LPDDR5,优化时序噪声。

- 射频/5G芯片:控制EMI和串扰。

- AI/处理器SoC:验证多核互连完整性。

- 汽车/工业芯片:耐环境干扰。

这些领域速率高、集成密,SI是可靠性基石。

相关行业标准

SI需遵守严格规范:

| 标准 | 适用芯片 | 关键要求示例 |

|---|---|---|

| PCIe Gen6 | 高速总线 | PAM4眼图TJ < 0.3 UI,IL预算紧 |

| USB4 | 接口芯片 | RL < -18 dB,串扰 < -30 dB |

| DDR5 | 内存 | 眼宽裕度,时序窗口>指定ps |

| JEDEC | 通用标准 | 阻抗匹配±10%,抖动分解 |

标准由PCI-SIG、USB-IF、JEDEC等制定。

测试步骤详解

标准SI测试流程:

- 准备:定义参数,准备芯片样品和仪器。

- 仿真:建模互连,预测风险。

- 实测:采集眼图、S参数、TDR数据。

- 分析:比对阈值,定位根因。

- 优化:调整布局或封装,重测验证。

过程需校准以确保精度。

真实案例分享

- AI芯片案例:某SoC抖动超标,经眼图测试发现串扰,优化走线间距后性能提升25%。

- 5G基带芯片:反射导致BER高,VNA分析定位封装不匹配,改进后顺利通过认证。

这些案例证明重视SI能化险为夷。

常见问题解答

- SI测试何时介入? 设计早期到量产验证全程。

- 成本高吗? 初期投入远低于后期修复。

- 与PI区别? SI侧重信号,PI关注电源;常联合测试。

- 未来趋势? AI辅助仿真,112G+ SerDes更严苛。

总结

芯片测试中越来越重视SI,是因为高速、高集成趋势放大了反射、串扰、抖动等风险,直接影响性能、可靠性和成本。从概念到应用,本文展示了SI测试的价值与实践。未来,随着6G和量子芯片兴起,SI将更关键。

如果您的芯片项目需SI评估或优化,上海德垲芯片检测(https://www.jiancechip.com)提供咨询+报告服务、行业标准支持以及定制化测试方案,欢迎联系获取专业指导。