在芯片设计与制造领域,随着数据传输速率不断提升至数十Gbps甚至更高,信号完整性(Signal Integrity,简称SI)已成为确保芯片性能稳定的关键环节。芯片测试中的SI评估聚焦于信号在高速传输过程中的质量,避免反射、串扰和抖动等因素导致的功能失效或误码率上升。本文将详解SI测试的主要参数、测量方法及实际应用,帮助工程师更好地理解和优化芯片设计。

信号完整性测试的概念

信号完整性测试是指在芯片互连系统中评估信号波形的保真度,确保信号从发送端到接收端的时序、幅度和形状不因物理因素而严重失真。它涉及时域和频域分析,核心目的是量化潜在问题,如阻抗不匹配或电磁干扰,从而指导芯片布局和封装优化。

主要测量参数

芯片SI测试的核心在于监测以下关键参数,这些指标直接反映信号质量:

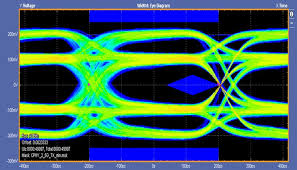

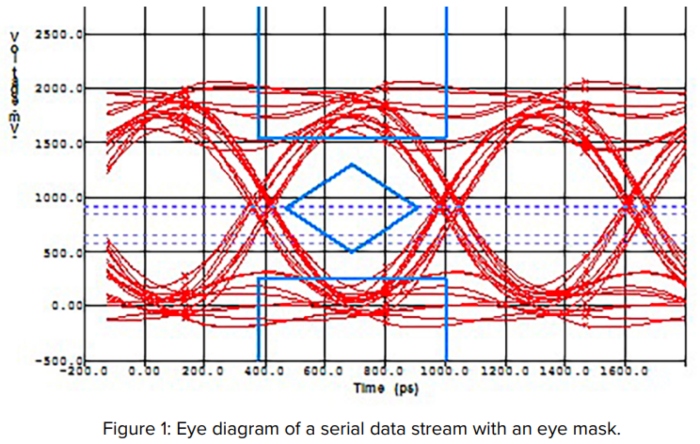

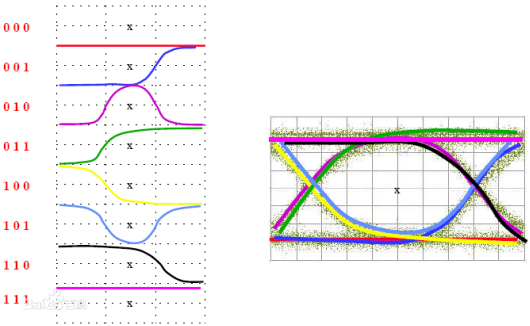

- 眼图参数:包括眼高(电压裕度)、眼宽(时序裕度)和眼图闭合程度,用于评估整体信号完整性。

- 抖动:总抖动(TJ)、随机抖动(RJ)和确定性抖动(DJ),测量时序不确定性。

- 反射与阻抗:回波损耗(RL)和阻抗连续性,检测阻抗不匹配。

- 串扰:近端串扰(NEXT)和远端串扰(FEXT),评估相邻信号干扰。

- 损耗:插入损耗(IL)和导体/介质损耗,量化信号幅度衰减。

- 上升/下降时间:边沿速率,影响高速信号的清晰度。

- 噪声水平:电源噪声和地弹,影响信号纯净度。

这些参数通过S参数模型统一描述,确保芯片在高频环境下的可靠传输。

为什么测量这些参数

忽略这些参数可能导致芯片在实际应用中出现间歇故障或性能瓶颈。例如,眼图裕度不足会增加误码率,而高串扰则干扰多通道并行操作。测量它们有助于在设计阶段预测问题,降低返工成本,并符合行业规范,确保芯片兼容性和稳定性。

参数测量种类

SI参数测量分为两大类:

时域测量

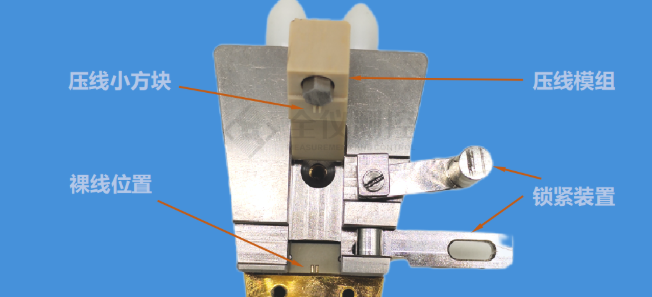

聚焦信号波形动态,包括TDR(时域反射计)用于阻抗和反射分析,以及眼图叠加评估抖动和裕度。

频域测量

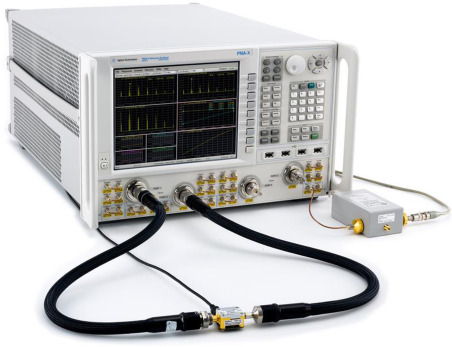

使用VNA(矢量网络分析仪)提取S参数,如S11(回波损耗)和S21(插入损耗),适合量化损耗和串扰。

这些种类互补,时域直观、频域精确。

测量方法

SI测试方法结合仿真与实测:

- 仿真工具:如HyperLynx或ADS软件,预分析参数风险。

- 实测仪器:高带宽示波器(>20GHz)和VNA,采集眼图、S参数数据。

- 过程:设置测试环境、注入标准信号、捕获波形、分析阈值合规。

方法需校准仪器以确保准确性,更多仪器选择可参考相关测试设备指南。

应用领域

在芯片测试中,SI参数测量广泛应用于:

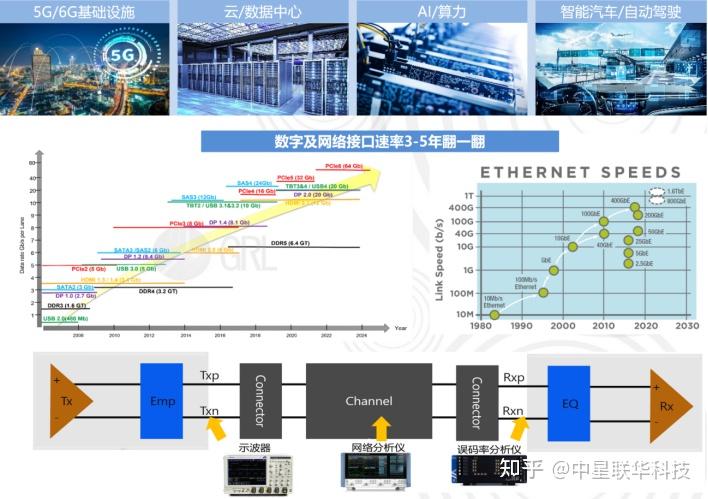

- 高速接口芯片:如PCIe、USB4,确保眼图和抖动达标。

- 内存模块:DDR5/LPDDR5,优化时序和噪声。

- 射频芯片:5G/6G,控制损耗和串扰。

- SoC集成:多核处理器,验证内部互连完整性。

这些领域强调参数与系统性能的直接关联。

相关行业标准

SI参数需符合特定标准,以下是典型示例:

| 标准 | 关键参数要求示例 | 适用芯片类型 |

|---|---|---|

| PCIe Gen6 | 抖动 < 0.3 UI,RL < -20 dB | 高速总线芯片 |

| USB4 | 眼宽裕度,IL < -15 dB | 接口芯片 |

| DDR5 | 眼高/眼宽,噪声容限 | 内存芯片 |

| OIF CEI | S参数预算,串扰 < -30 dB | 光模块芯片 |

标准由USB-IF、PCI-SIG等组织制定,确保芯片互操作性。

测试步骤详解

标准SI参数测量流程如下:

- 准备阶段:定义参数阈值、准备芯片样品和仪器。

- 仿真验证:建模链路,预测眼图和S参数。

- 实测执行:注入信号,采集数据如眼图和抖动。

- 数据分析:比对标准,定位问题如反射源。

- 优化迭代:调整设计,重测参数合规。

真实案例分享

- PCIe芯片案例:某SoC眼图闭合严重,经VNA测量发现回波损耗超标,优化阻抗后参数达标,误码率降至10^-12。

- 5G模块案例:串扰导致抖动高,通过TDR定位走线问题,调整后噪声水平改善,芯片顺利通过认证。

这些案例展示参数测量在故障诊断中的作用。

常见问题解答

- 哪些参数最关键? 眼图和抖动,通常决定芯片整体性能。

- 测试周期多久? 视复杂度,1-7天。

- 如何选择仪器? 根据芯片速率选带宽充足的示波器和VNA。

- 参数异常如何处理? 分析根因,如调整层叠或添加去耦。

更多疑问可查阅检测百科。

总结

芯片测试中的信号完整性主要测量眼图、抖动、反射、串扰、损耗等参数,这些指标确保高速信号的可靠传输。从概念到步骤,本文覆盖了SI测试的全貌,帮助工程师避免常见 pitfalls 并优化设计。

如果您在芯片项目中需专业SI参数评估,上海德垲芯片检测(https://www.jiancechip.com)提供咨询+报告服务、行业标准支持以及定制化测试方案,欢迎联系获取优化指导。