随着 5G 通信、人工智能及高性能计算技术的飞速发展,芯片内部及芯片间的数据传输速率不断提升,高速接口已成为现代半导体产品的核心组成部分。确保这些接口在极端工况下的信号完整性与通信稳定性,直接关系到终端产品的性能表现与用户体验。芯片高速接口测试不仅是验证设计合规性的必要环节,更是保障产品长期可靠运行的关键防线。

高速接口测试的核心范畴

高速接口测试主要针对芯片中用于高带宽数据传输的物理层链路进行验证。测试范围覆盖从发送端驱动器到接收端均衡器的完整信号路径,旨在发现潜在的信号失真、时序偏差及干扰问题。根据应用场景的不同,测试对象通常包括处理器、存储器、通信模块及各类接口控制器。

主流协议覆盖

不同的应用领域对应着各异的高速传输协议,测试方案需严格遵循相应标准组织制定的规范。常见的测试协议包括但不限于:

- PCIe 系列:广泛应用于计算机及服务器的扩展接口,测试重点在于链路训练与均衡。

- USB 系列:消费类电子产品的通用连接标准,侧重兼容性与供电稳定性验证。

- DDR 内存接口:决定系统数据吞吐能力,需关注时序余量与信号眼图质量。

- Ethernet 以太网:网络通信基础,涉及多种速率等级的物理层一致性测试。

关键测试指标详解

在高速信号传输过程中,多个物理参数直接影响通信质量。测试工程师需借助高精度仪器捕捉微小信号变化,并对关键指标进行量化评估。以下表格列出了核心测试参数及其定义:

| 测试指标 | 定义说明 | 重要性 |

|---|---|---|

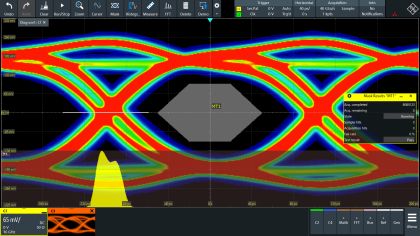

| 眼图(Eye Diagram) | 叠加多个信号周期形成的图形,反映信号质量 | 直观展示噪声、抖动及幅度损失 |

| 抖动(Jitter) | 信号边沿相对于理想位置的时序偏差 | 过大会导致误码率上升,影响同步 |

| 插入损耗(Insertion Loss) | 信号通过传输通道后的能量衰减 | 决定信号传输距离与高频性能 |

| 回波损耗(Return Loss) | 信号反射回来的能量比例 | 反映阻抗匹配程度,影响信号完整性 |

测试流程与难点

实施芯片高速接口测试需要严谨的流程控制与专业的环境搭建。从测试计划制定到最终报告输出,每个环节都需精确执行,以排除外部干扰对测试结果的影响。

信号完整性挑战

随着传输速率突破 GHz 级别,信号完整性问题愈发凸显。趋肤效应、介质损耗及串扰等因素会导致信号波形严重畸变。测试过程中,需采用去嵌入技术去除夹具影响,并利用均衡算法模拟接收端补偿效果。此外,电源噪声耦合也是常见干扰源,需配合电源完整性测试共同分析,确保参考平面的稳定性。

测试价值与趋势

通过专业的高速接口测试,企业能够在量产前识别设计缺陷,降低后期改版成本。随着技术发展,测试速率不断攀升,对仪器带宽及探头精度提出了更高要求。未来测试方案将更加注重自动化与智能化,结合仿真数据与实测结果进行 корреляция 分析,进一步提升验证效率与覆盖率。高质量的测试服务已成为芯片企业通过车规级认证及进入高端供应链的必备条件。

关于上海德垲检测

上海德垲检测作为一家专业的第三方检测机构,深耕半导体测试领域多年。公司拥有先进的实验室环境,配备高精度示波器、误码仪及矢量网络分析仪等高端设备,能够满足 PCIe、USB、DDR 等多种高速协议的测试需求。技术团队具备丰富的芯片测试开发经验,擅长处理复杂的信号完整性问题与失效分析案例。无论是可靠性验证还是专业测试服务,德垲检测都能提供定制化解决方案,助力客户产品快速通过认证。

欢迎联系专业工程师,获取详细的测试方案与技术支持,共同保障芯片产品的高质量交付。